- すべてのカテゴリ

- 集積回路(IC)

- 開発ボード、キット、プログラマ

- ディスクリート半導体製品

- 電源 - 基板実装

- RFおよびワイヤレス

- センサ、トランスデューサ

- メモリカード、モジュール

- オーディオ製品

- 回路保護

- 水晶、発振器、共振器

- フィルター

- アイソレーター

- キット

- メーカー/DIY, 教育

- オプトエレクトロニクス

- 電源 - 外部/内部(基板外)

- リレー

- 抵抗器

- 試験と測定

- 未分類

- コネクタ、相互接続

- インダクタ、コイル、チョーク

- モータ、アクチュエータ、ソレノイド、ドライバ

- スイッチ

- ケーブルアセンブリ

- 組み込みコンピュータ

- コンデンサ

- ファン、熱管理

- トランスフォーマー

- バッテリー製品

- 製品

- すべてのカテゴリ

-

集積回路(IC)

- 埋め込み

- インターフェース

- メモリー

-

パワーマネージメント(PMIC)

- DCスイッチングコントローラ

- ディスプレイドライバ

- フルハーフブリッジドライバー

- ゲートドライバー

- LEDドライバ

- モータドライバ、コントローラ

- 配電スイッチ、負荷ドライバ

- パワーマネージメント

- 電源コントローラ、モニタ

- 特別目的レギュレーター

- 監督

- 電圧レギュレータ - 直流DCスイッチングレギュレータ

- 電圧レギュレータ - リニア

- 電圧レギュレータ - リニア + スイッチング

- AC DCコンバータ、オフラインスイッチ

- バッテリーチャージャー

- バッテリー管理

- 現在の規制/管理

- エネルギー計測

- ホットスワップコントローラ

- レーザードライバー

- 照明、バラストコントローラ

- ORコントローラ、理想ダイオード

- PFC(力率改善)

- PoE(Power Over Ethernet)コントローラ

- RMS-DCコンバータ

- 熱管理

- 電圧リファレンス

- 電圧レギュレータ - リニアレギュレータコントローラ

- V/FおよびF/Vコンバータ

- 特殊IC

- オーディオ特殊用途

- クロック/タイミング

- データ収集

- リニア

- ロジック

-

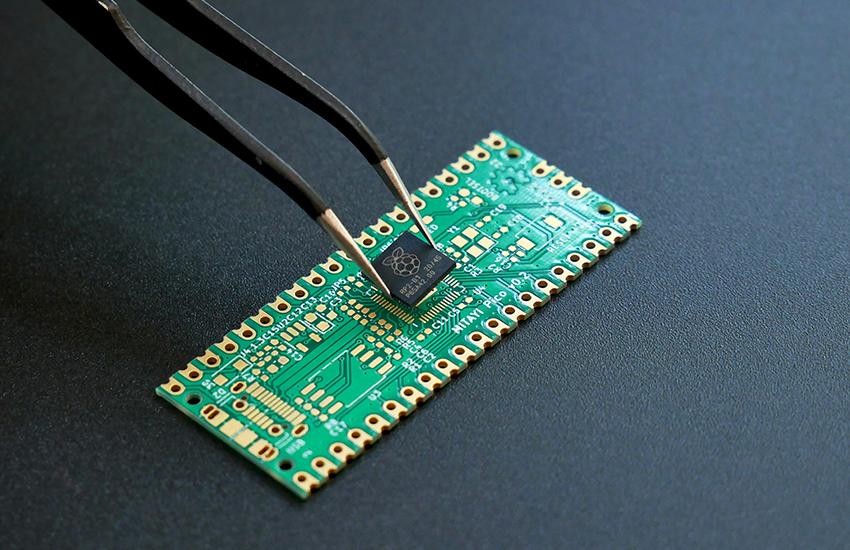

開発ボード、キット、プログラマ

- アクセサリー

- 評価・デモボードとキット

- 評価ボード - DC/DC & AC/DC(オフライン)SMPS

- 評価ボード - 拡張ボード、ドーターカード

- 評価ボード - LEDドライバ

- 評価ボード - センサー

- 評価ボード - エンベデッド - 複雑なロジック(FPGA、CPLD)

- 評価ボード - 組み込み - MCU、DSP

- プログラマ、エミュレータ、デバッガ

- ソフトウェア、サービス

- 評価ボード - アナログ/デジタルコンバータ(ADC)

- 評価ボード - オーディオアンプ

- 評価ボード - デジタル/アナログコンバータ(DAC)

- 評価ボード - リニア電圧レギュレータ

- 評価ボード - オペアンプ

- プログラミングアダプタ、ソケット

- RF評価および開発キット、ボード

- RFID評価および開発キット、ボード

- ディスクリート半導体製品

- 電源 - 基板実装

-

RFおよびワイヤレス

- RFアンプ

- アッテネーター

- RFアクセサリー

- RF復調器

- RFディテクター

- RFフロントエンド(LNA + PA)

- RFその他ICおよびモジュール

- RFミキサー

- RF変調器

- RFパワーコントローラIC

- RFパワー・デバイダ/スプリッタ

- RFレシーバー

- RFシールド

- RFスイッチ

- RFトランシーバIC

- RFトランシーバモジュールとモデム

- RFトランスミッター

- RFID、RFアクセス、監視IC

- RFIDトランスポンダ、タグ

- RFマルチプレクサ

- RFレシーバー、トランスミッター、トランシーバー完成品ユニット

- RFアンテナ

- RFIおよびEMI - コンタクト、フィンガーストックおよびガスケット

- RFIDリーダーモジュール

- RFサーキュレータとアイソレータ

- RF方向性結合器

- バラン

- 加入者識別モジュール(SIM)カード

- RFIDアクセサリー

- RFIDアンテナ

-

センサ、トランスデューサ

- メモリカード、モジュール

- オーディオ製品

- 回路保護

- 水晶、発振器、共振器

- フィルター

- アイソレーター

- キット

- メーカー/DIY, 教育

-

オプトエレクトロニクス

- 回路基板インジケータ、アレイ、ライトバー、棒グラフ

- 光トランシーバモジュール

- LED文字と数字

- COB、エンジン、モジュール、ストリップ

- カラーLED照明

- ディスプレイベゼル、レンズ

- 光ファイバーレシーバー

- 光ファイバートランスミッタ - ディスクリート

- 光ファイバートランスミッタ - ドライブ回路内蔵

- レーザーダイオード、モジュール

- LEDドットマトリクスとクラスタ

- LEDエミッター - 赤外線、紫外線、可視光線

- LED表示 - ディスクリート

- レンズ

- オプトエレクトロニクス・アクセサリー

- 白色LED照明

- 白熱灯、ネオンランプ

- 光ファイバースイッチ、マルチプレクサ、デマルチプレクサ

- バラスト、インバータ

- LCD、OLED、グラフィック

- LCD、OLED 文字および数字

- ディスプレイ、モニタ - LCDドライバ/コントローラ

- 電源 - 外部/内部(基板外)

- リレー

- 抵抗器

- 試験と測定

- 未分類

- コネクタ、相互接続

- インダクタ、コイル、チョーク

- モータ、アクチュエータ、ソレノイド、ドライバ

- スイッチ

- ケーブルアセンブリ

- 組み込みコンピュータ

- コンデンサ

- ファン、熱管理

- トランスフォーマー

- バッテリー製品

- メーカー

- サービス

- 産業

- 最高品質へのこだわり

- リソース

LCMXO2-1200ZE-P1-EVN datasheet

LCMXO2-1200ZE-P1-EVN pdf

LCMXO2-1200ZE-P1-EVN distributor

LCMXO2-1200ZE-P1-EVN manufacturer

LCMXO2-1200ZE-P1-EVN supplier

LCMXO2-1200ZE-P1-EVN price

LCMXO2-1200ZE-P1-EVN specification

LCMXO2-1200ZE-P1-EVN wholesale

LCMXO2-1200ZE-P1-EVN package

LCMXO2-1200ZE-P1-EVN Lattice Semiconductor Corporation

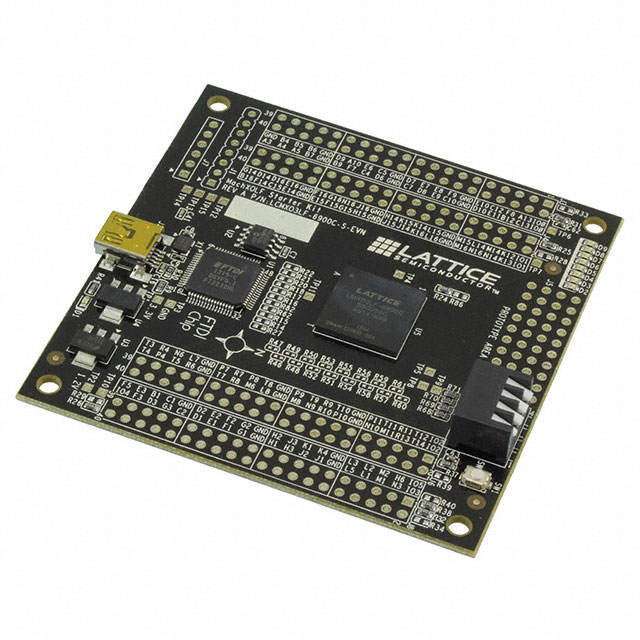

LCMXO2-1200ZE-P1-EVN

¥13074.19

価格更新:ヶ月前

Lattice Semiconductor Corporation

ラティスセミコンダクターは低消費電力プログラマビリティをリードし、エッジからクラウドまで、ネットワーク全体の複雑な課題を解決します。通信、コンピューティング、産業、自動車、コンシューマに足がかりを持つラティスセミコンダクターは、持続的な関係を育み、自由なイノベーションのための世界クラスのサポートを提供し、安全で接続された世界を作り上げます。

すべての製品を見る Lattice Semiconductor Corporation人気の商品

Feature

Flexible Logic Architecture

• Six devices with 256 to 6864 LUT4s and 19 to 335 I/Os

Ultra Low Power Devices

• Advanced 65 nm low power process

• As low as 19 µW standby power

• Programmable low swing differential I/Os

• Stand-by mode and other power saving options

Embedded and Distributed Memory

• Up to 240 Kbits sysMEM™ Embedded Block RAM

• Up to 54 Kbits Distributed RAM

• Dedicated FIFO control logic

On-Chip User Flash Memory

• Up to 256 Kbits of User Flash Memory

• 100,000 write cycles

• Accessible through WISHBONE, SPI, I2 C and JTAG interfaces

• Can be used as soft processor PROM or as Flash memory

Pre-Engineered Source Synchronous I/O

• DDR registers in I/O cells

• Dedicated gearing logic

• 7:1 Gearing for Display I/Os

• Generic DDR, DDRX2, DDRX4

• Dedicated DDR/DDR2/LPDDR memory with DQS support

High Performance, Flexible I/O Buffer

• Programmable sysIO™ buffer supports wide range of interfaces:

– LVCMOS 3.3/2.5/1.8/1.5/1.2

– LVTTL

– PCI

– LVDS, Bus-LVDS, MLVDS, RSDS, LVPECL

– SSTL 25/18

– HSTL 18

– Schmitt trigger inputs, up to 0.5V hysteresis

• I/Os support hot socketing

• On-chip differential termination

• Programmable pull-up or pull-down mode

Flexible On-Chip Clocking

• Eight primary clocks

• Up to two edge clocks for high-speed I/O interfaces (top and bottom sides only)

• Up to two analog PLLs per device with fractional-n frequency synthesis – Wide input frequency range (10 MHz to 400 MHz)

Non-volatile, Infinitely Reconfigurable

• Instant-on – powers up in microseconds

• Single-chip, secure solution

• Programmable through JTAG, SPI or I2 C

• Supports background programming of non-volatile memory

• Optional dual boot with external SPI memory

TransFR™ Reconfiguration

• In-field logic update while system operates

Enhanced System Level Support

• On-chip hardened functions: SPI, I2 C, timer/ counter

• On-chip oscillator with 5.5% accuracy

• Unique TraceID for system tracking

• One Time Programmable (OTP) mode

• Single power supply with extended operating range

• IEEE Standard 1149.1 boundary scan

• IEEE 1532 compliant in-system programming

Broad Range of Package Options

• TQFP, WLCSP, ucBGA, csBGA, caBGA, ftBGA, fpBGA, QFN package options

• Small footprint package options – As small as 2.5x2.5mm

• Density migration supported

• Advanced halogen-free packaging

- 1. 送料は 40 ドルから始まりますが、南アフリカ、ブラジル、インド、パキスタン、イスラエルなどの特定の国では価格が異なる場合があります。

- 2. 0.5kg以下または同等の荷物の基本運賃は、タイムゾーンと国によって影響されます。

- 1. 当社の製品は現在、DHL、SF、UPS を使用して発送されています。数量が少ない場合は、FedEx が選ばれる運送業者です。

- 1. 発送後の配達予定時間は、選択した配送方法によって異なります。

SZCの物流および在庫管理プログラムは、前例のない成功をもたらします。

福田、龍崗、南山にある戦略的ハブは、特定の顧客ニーズに対応したさまざまなカスタマイズプログラムを提供しています。

また、主要な物流キャリアとの長期的な関係を築き、お客様の個々の要件に対応する柔軟なソリューションを提供しています。

1. 当社から購入されたすべての電子部品には、365日間の保証が付いています。当社は製品の品質を保証します。

2. 完璧な状態でない商品を受け取った場合、責任を持って返金または交換を手配します。ただし、これらのオプションを利用するためには、商品が元の状態である必要があります。

FAQs:

Q: SZコンポーネントはどのようにしてLCMXO2-1200ZE-P1-EVNが本物のによって製造または配布されているかを確認していますか?

A: 当社の専門的なビジネス開発部門は、の元の製造業者および代理店の資格を厳格にテストおよび検証しています。すべてのの供給業者は、当社のプラットフォームにLCMXO2-1200ZE-P1-EVNデバイスを掲載する前に、資格レビューに合格する必要があります。当社は、LCMXO2-1200ZE-P1-EVN製品の調達チャネルと品質を何よりも優先し、徹底したサプライヤー監査を行っていますので、最大限の信頼を持って購入することができます。

Q: LCMXO2-1200ZE-P1-EVNチップの詳細情報、元の製造業者の詳細、評価ボード - エンベデッド - 複雑なロジック(FPGA、CPLD)アプリケーション、画像などはどこで見ることができますか?

A: SZコンポーネントのインテリジェント検索エンジンを利用して、評価ボード - エンベデッド - 複雑なロジック(FPGA、CPLD)カテゴリでフィルタリングするか、のブランドページをナビゲートして、包括的な情報を入手してください。

Q: のLCMXO2-1200ZE-P1-EVNの価格と在庫レベルはプラットフォーム上で正確ですか?

A: の在庫には大きな変動があるため、リアルタイムの更新は困難です。しかし、24時間以内に定期的な更新を行っています。支払いを進める前に、SZコンポーネントの営業担当者またはオンラインカスタマーサービスを通じてLCMXO2-1200ZE-P1-EVNの注文を確認することをお勧めします。

Q: SZコンポーネントで受け入れられる支払い方法は何ですか?

A: TT銀行、PayPal、クレジットカード、ウェスタンユニオン、エスクローなど、さまざまな支払い方法を受け入れています。

Q: 配送の手配はどのように行われ、荷物の追跡はどのように行いますか?

A: 顧客はDHL、FedEx、UPS、TNT、登録メールなど、業界をリードする運送会社から選択することができます。ご注文が出荷の準備が整い次第、営業チームから配送の詳細をお知らせし、追跡番号を提供します。追跡情報が表示されるまでに最大24時間かかることがあります。通常、エクスプレス配送は3-5日、登録メールは25-60日かかります。

Q: LCMXO2-1200ZE-P1-EVNの返品または交換の手続きはどのように行われますか?

A: 出荷前検査(PSI)を注文のランダムに選ばれたバッチに対して行い、出荷前の品質を確保しています。以下の条件の下でLCMXO2-1200ZE-P1-EVNがご期待に沿わない場合、返品または交換を受け付けます:

- 間違った数量の発送、誤ったアイテムの配送、または明らかな外部欠陥などの問題が当社によって認められた場合。

- 配送日から90日以内に欠陥を通知された場合。

- LCMXO2-1200ZE-P1-EVNが未使用のまま元の梱包である場合。

- 返品を開始するには、以下を行ってください:

- 90日間の期間内に通知してください。

- 返品承認のリクエストを取得してください。

- 詳細については、当社の返品および交換ポリシーを参照してください。

Q: LCMXO2-1200ZE-P1-EVNのデータシートやピン図などのサポートをどのようにして入手できますか?

A: LCMXO2-1200ZE-P1-EVNのデータシートやピン図など、アフターサービスに関するお問い合わせは、[email protected]までお気軽にご連絡ください。

Q: SZコンポーネントにどのように連絡しますか?具体的な連絡方法を教えてください。

A: 当サイトの右下隅にあるカスタマーサービスボタンをクリックするか、直接RFQを送信するか、またはページ上部の「お問い合わせ」リンクを使用してメールを送信するか、お電話でお問い合わせください。24時間以内にお問い合わせに対応します。

製品の属性

| TYPE | 説明 | すべて選択 |

|---|---|---|

| シリーズ | マッハXO2 | |

| パッケージ | 箱 | |

| 製品ステータス | アクティブ | |

| タイプ | FPGA | |

| 併用/関連製品 | LCMXO2-1200 | |

| プラットフォーム | MachXO2 FPGA ピコ | |

| 内容 | ボード、ケーブル、電源 |

ブログ

XC6SLX4とXC6SLX9:どちらが優れているか?XC6SLX4およびXC6SLX9 FPGAのポテンシャルを活用し、性能と汎用性を強化。

XC6SLX4とXC6SLX9:どちらが優れているか?XC6SLX4およびXC6SLX9 FPGAのポテンシャルを活用し、性能と汎用性を強化。 米国のマイクロコントローラー・メーカー上位10社エレクトロニクスを形作るトッププレーヤーを明らかにする、米国のマイクロコントローラ技術革新トップ10をご覧ください。ゲームを変える旅に出かけよう!

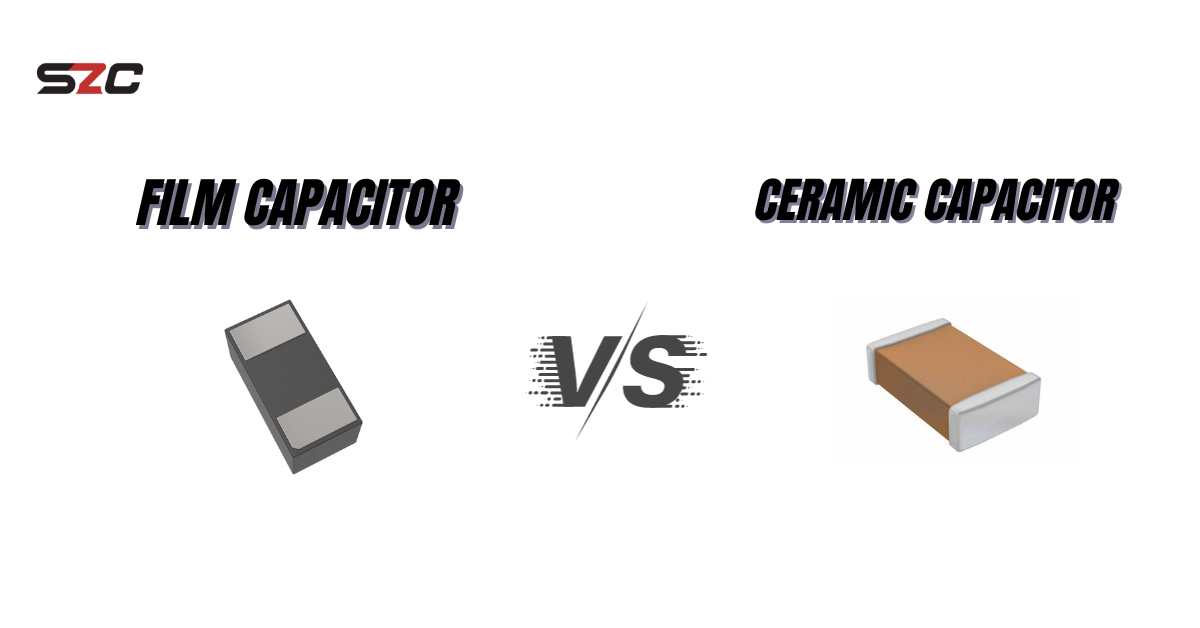

米国のマイクロコントローラー・メーカー上位10社エレクトロニクスを形作るトッププレーヤーを明らかにする、米国のマイクロコントローラ技術革新トップ10をご覧ください。ゲームを変える旅に出かけよう! フィルム対セラミック:適切なコンデンサの選択フィルムコンデンサとセラミックコンデンサを解明しながら、電子部品の世界を探検しましょう。この技術マニア向けのガイドブックで、キャパシタンスの流れを探る魅惑の旅に出かけましょう。

フィルム対セラミック:適切なコンデンサの選択フィルムコンデンサとセラミックコンデンサを解明しながら、電子部品の世界を探検しましょう。この技術マニア向けのガイドブックで、キャパシタンスの流れを探る魅惑の旅に出かけましょう。 米国のRFミキサーメーカートップ10を探るアメリカのRFミキサーメーカートップ10を発見する準備はできましたか?技術革新の旅に出かけましょう。

米国のRFミキサーメーカートップ10を探るアメリカのRFミキサーメーカートップ10を発見する準備はできましたか?技術革新の旅に出かけましょう。 SZComponentsが「国際潜在的スターディストリビューター」賞を受賞賞SZComponentsの「国際的な潜在力を秘めたスター・ディストリビューター」としての目覚ましい受賞を祝い、彼らの成功への道のりを探ります。

SZComponentsが「国際潜在的スターディストリビューター」賞を受賞賞SZComponentsの「国際的な潜在力を秘めたスター・ディストリビューター」としての目覚ましい受賞を祝い、彼らの成功への道のりを探ります。

未来を解き明かす:2024年に急増するマイコンダイナミックな電子部品の世界において、マイクロコントローラは革新性と汎用性の証として際立っています。2024年に近づくにつれ、STマイクロエレクトロニクス、テキサス・インスツルメンツ、マイクロチップなどの大企業が先導するマイクロコントローラと半導体の状況は、著しい変化を遂げようとしています。

未来を解き明かす:2024年に急増するマイコンダイナミックな電子部品の世界において、マイクロコントローラは革新性と汎用性の証として際立っています。2024年に近づくにつれ、STマイクロエレクトロニクス、テキサス・インスツルメンツ、マイクロチップなどの大企業が先導するマイクロコントローラと半導体の状況は、著しい変化を遂げようとしています。 マイクロコントローラ vs. マイクロプロセッサ:組込みシステム工学のためのコアの違いを解き明かす組込みシステムエンジニアリングやエレクトロニクス分野の製品開発に精通した専門家は、マイクロコントローラとマイクロプロセッサの区別に悩むことが多い。無数の電子機器の設計と製造において基本的な役割を担っているにもかかわらず、単なる定義に基づいてその独自の機能を理解することは困難です:

マイクロコントローラ vs. マイクロプロセッサ:組込みシステム工学のためのコアの違いを解き明かす組込みシステムエンジニアリングやエレクトロニクス分野の製品開発に精通した専門家は、マイクロコントローラとマイクロプロセッサの区別に悩むことが多い。無数の電子機器の設計と製造において基本的な役割を担っているにもかかわらず、単なる定義に基づいてその独自の機能を理解することは困難です: セラミックコンデンサの世界市場を深堀する世界のセラミックコンデンサ市場における環境意識の新たなサブプロットを探る。

セラミックコンデンサの世界市場を深堀する世界のセラミックコンデンサ市場における環境意識の新たなサブプロットを探る。 マイクロコントローラで電流測定をマスターするマイクロコントローラーで正確な電流測定の秘密を解き明かす!オンチップ・アナログ・コア独立ペリフェラル(CIP)で課題を克服し、超人的なソリューションを実現し、精度に革命をもたらします。

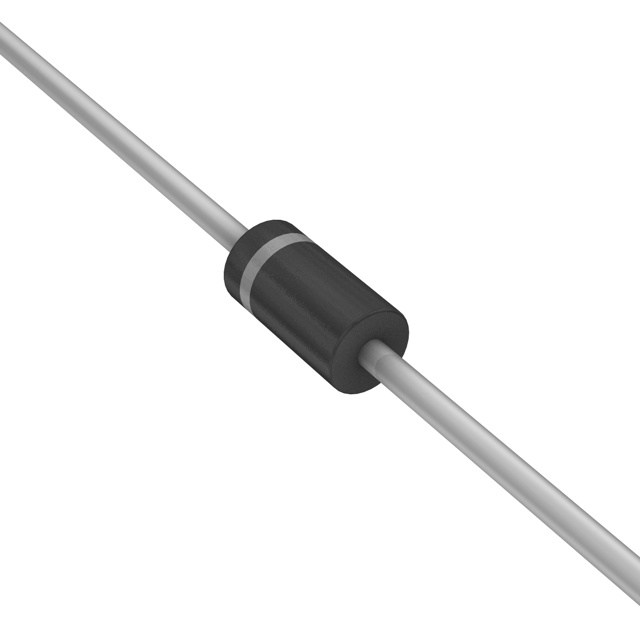

マイクロコントローラで電流測定をマスターするマイクロコントローラーで正確な電流測定の秘密を解き明かす!オンチップ・アナログ・コア独立ペリフェラル(CIP)で課題を克服し、超人的なソリューションを実現し、精度に革命をもたらします。 整流ダイオードとは?初心者向けガイドエレクトロニクスの縁の下の力持ち、整流ダイオード!整流ダイオードの魔力、アプリケーションを探求し、ガジェット・パワーへの舞台裏の冒険に参加しよう。

整流ダイオードとは?初心者向けガイドエレクトロニクスの縁の下の力持ち、整流ダイオード!整流ダイオードの魔力、アプリケーションを探求し、ガジェット・パワーへの舞台裏の冒険に参加しよう。

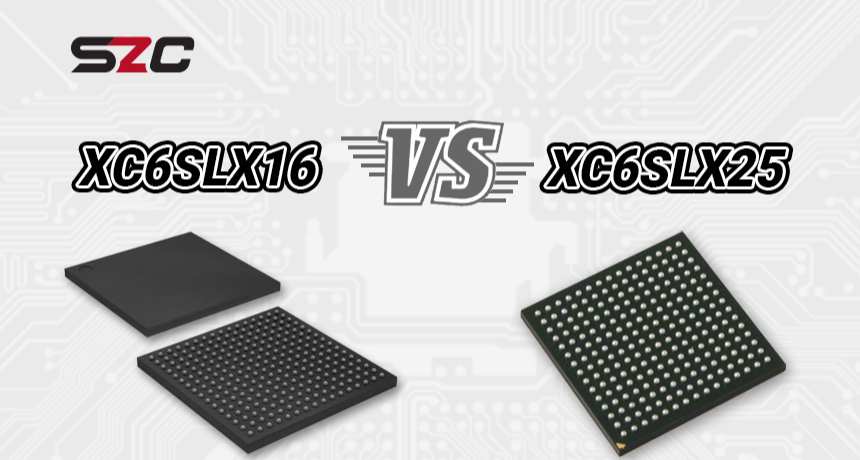

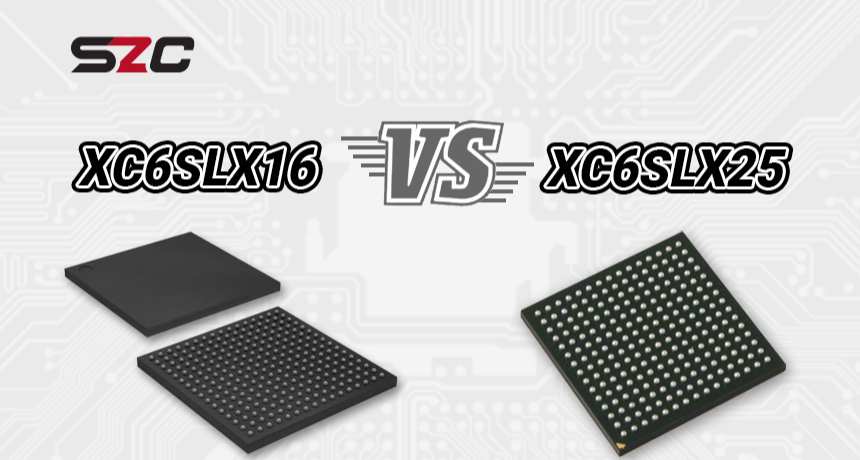

FPGA対決:XC6SLX16 vs XC6SLX25クイックガイドでFPGAの秘密を解き明かすXC6SLX16とXC6SLX25、次の技術的冒険の鍵はどちらに?今すぐクリックして、プログラマブルな可能性の世界を探検してください!

FPGA対決:XC6SLX16 vs XC6SLX25クイックガイドでFPGAの秘密を解き明かすXC6SLX16とXC6SLX25、次の技術的冒険の鍵はどちらに?今すぐクリックして、プログラマブルな可能性の世界を探検してください! オンセミの先進画像センサーで交通安全を強化onsemiのAR0220ATは、先進運転支援システムの夜間の常識を覆します。

オンセミの先進画像センサーで交通安全を強化onsemiのAR0220ATは、先進運転支援システムの夜間の常識を覆します。 テキサス・インスツルメンツ、ユタ州リーハイを最先端半導体ハブに選定テキサス・インスツルメンツ(TI)社は、ユタ州リーハイを300ミリ半導体ウェハ製造工場(ファブ)の建設予定地に選んだ。

テキサス・インスツルメンツ、ユタ州リーハイを最先端半導体ハブに選定テキサス・インスツルメンツ(TI)社は、ユタ州リーハイを300ミリ半導体ウェハ製造工場(ファブ)の建設予定地に選んだ。 SZComponentsからの感謝祭のご挨拶SZComponentsファミリーの一員であることに感謝します。感謝祭おめでとうございます!

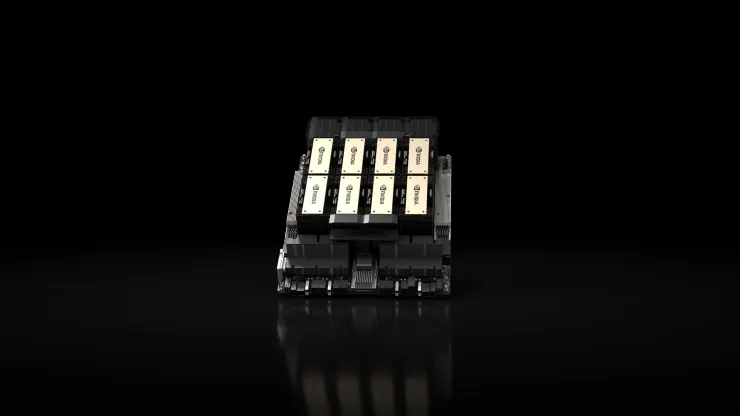

SZComponentsからの感謝祭のご挨拶SZComponentsファミリーの一員であることに感謝します。感謝祭おめでとうございます! AIモデル・トレーニングのためのNvidia H200のパワーを発見するNvidiaのH200チップで、AIトレーニングの最先端の可能性を発見してください。AIモデルの究極の可能性を引き出し、仕事に革命を起こしましょう。

AIモデル・トレーニングのためのNvidia H200のパワーを発見するNvidiaのH200チップで、AIトレーニングの最先端の可能性を発見してください。AIモデルの究極の可能性を引き出し、仕事に革命を起こしましょう。

XC6SLX4とXC6SLX9:どちらが優れているか?XC6SLX4およびXC6SLX9 FPGAのポテンシャルを活用し、性能と汎用性を強化。

XC6SLX4とXC6SLX9:どちらが優れているか?XC6SLX4およびXC6SLX9 FPGAのポテンシャルを活用し、性能と汎用性を強化。 米国のマイクロコントローラー・メーカー上位10社エレクトロニクスを形作るトッププレーヤーを明らかにする、米国のマイクロコントローラ技術革新トップ10をご覧ください。ゲームを変える旅に出かけよう!

米国のマイクロコントローラー・メーカー上位10社エレクトロニクスを形作るトッププレーヤーを明らかにする、米国のマイクロコントローラ技術革新トップ10をご覧ください。ゲームを変える旅に出かけよう! フィルム対セラミック:適切なコンデンサの選択フィルムコンデンサとセラミックコンデンサを解明しながら、電子部品の世界を探検しましょう。この技術マニア向けのガイドブックで、キャパシタンスの流れを探る魅惑の旅に出かけましょう。

フィルム対セラミック:適切なコンデンサの選択フィルムコンデンサとセラミックコンデンサを解明しながら、電子部品の世界を探検しましょう。この技術マニア向けのガイドブックで、キャパシタンスの流れを探る魅惑の旅に出かけましょう。 米国のRFミキサーメーカートップ10を探るアメリカのRFミキサーメーカートップ10を発見する準備はできましたか?技術革新の旅に出かけましょう。

米国のRFミキサーメーカートップ10を探るアメリカのRFミキサーメーカートップ10を発見する準備はできましたか?技術革新の旅に出かけましょう。 SZComponentsが「国際潜在的スターディストリビューター」賞を受賞賞SZComponentsの「国際的な潜在力を秘めたスター・ディストリビューター」としての目覚ましい受賞を祝い、彼らの成功への道のりを探ります。

SZComponentsが「国際潜在的スターディストリビューター」賞を受賞賞SZComponentsの「国際的な潜在力を秘めたスター・ディストリビューター」としての目覚ましい受賞を祝い、彼らの成功への道のりを探ります。

未来を解き明かす:2024年に急増するマイコンダイナミックな電子部品の世界において、マイクロコントローラは革新性と汎用性の証として際立っています。2024年に近づくにつれ、STマイクロエレクトロニクス、テキサス・インスツルメンツ、マイクロチップなどの大企業が先導するマイクロコントローラと半導体の状況は、著しい変化を遂げようとしています。

未来を解き明かす:2024年に急増するマイコンダイナミックな電子部品の世界において、マイクロコントローラは革新性と汎用性の証として際立っています。2024年に近づくにつれ、STマイクロエレクトロニクス、テキサス・インスツルメンツ、マイクロチップなどの大企業が先導するマイクロコントローラと半導体の状況は、著しい変化を遂げようとしています。 マイクロコントローラ vs. マイクロプロセッサ:組込みシステム工学のためのコアの違いを解き明かす組込みシステムエンジニアリングやエレクトロニクス分野の製品開発に精通した専門家は、マイクロコントローラとマイクロプロセッサの区別に悩むことが多い。無数の電子機器の設計と製造において基本的な役割を担っているにもかかわらず、単なる定義に基づいてその独自の機能を理解することは困難です:

マイクロコントローラ vs. マイクロプロセッサ:組込みシステム工学のためのコアの違いを解き明かす組込みシステムエンジニアリングやエレクトロニクス分野の製品開発に精通した専門家は、マイクロコントローラとマイクロプロセッサの区別に悩むことが多い。無数の電子機器の設計と製造において基本的な役割を担っているにもかかわらず、単なる定義に基づいてその独自の機能を理解することは困難です: セラミックコンデンサの世界市場を深堀する世界のセラミックコンデンサ市場における環境意識の新たなサブプロットを探る。

セラミックコンデンサの世界市場を深堀する世界のセラミックコンデンサ市場における環境意識の新たなサブプロットを探る。 マイクロコントローラで電流測定をマスターするマイクロコントローラーで正確な電流測定の秘密を解き明かす!オンチップ・アナログ・コア独立ペリフェラル(CIP)で課題を克服し、超人的なソリューションを実現し、精度に革命をもたらします。

マイクロコントローラで電流測定をマスターするマイクロコントローラーで正確な電流測定の秘密を解き明かす!オンチップ・アナログ・コア独立ペリフェラル(CIP)で課題を克服し、超人的なソリューションを実現し、精度に革命をもたらします。 整流ダイオードとは?初心者向けガイドエレクトロニクスの縁の下の力持ち、整流ダイオード!整流ダイオードの魔力、アプリケーションを探求し、ガジェット・パワーへの舞台裏の冒険に参加しよう。

整流ダイオードとは?初心者向けガイドエレクトロニクスの縁の下の力持ち、整流ダイオード!整流ダイオードの魔力、アプリケーションを探求し、ガジェット・パワーへの舞台裏の冒険に参加しよう。

FPGA対決:XC6SLX16 vs XC6SLX25クイックガイドでFPGAの秘密を解き明かすXC6SLX16とXC6SLX25、次の技術的冒険の鍵はどちらに?今すぐクリックして、プログラマブルな可能性の世界を探検してください!

FPGA対決:XC6SLX16 vs XC6SLX25クイックガイドでFPGAの秘密を解き明かすXC6SLX16とXC6SLX25、次の技術的冒険の鍵はどちらに?今すぐクリックして、プログラマブルな可能性の世界を探検してください! オンセミの先進画像センサーで交通安全を強化onsemiのAR0220ATは、先進運転支援システムの夜間の常識を覆します。

オンセミの先進画像センサーで交通安全を強化onsemiのAR0220ATは、先進運転支援システムの夜間の常識を覆します。 テキサス・インスツルメンツ、ユタ州リーハイを最先端半導体ハブに選定テキサス・インスツルメンツ(TI)社は、ユタ州リーハイを300ミリ半導体ウェハ製造工場(ファブ)の建設予定地に選んだ。

テキサス・インスツルメンツ、ユタ州リーハイを最先端半導体ハブに選定テキサス・インスツルメンツ(TI)社は、ユタ州リーハイを300ミリ半導体ウェハ製造工場(ファブ)の建設予定地に選んだ。 SZComponentsからの感謝祭のご挨拶SZComponentsファミリーの一員であることに感謝します。感謝祭おめでとうございます!

SZComponentsからの感謝祭のご挨拶SZComponentsファミリーの一員であることに感謝します。感謝祭おめでとうございます! AIモデル・トレーニングのためのNvidia H200のパワーを発見するNvidiaのH200チップで、AIトレーニングの最先端の可能性を発見してください。AIモデルの究極の可能性を引き出し、仕事に革命を起こしましょう。

AIモデル・トレーニングのためのNvidia H200のパワーを発見するNvidiaのH200チップで、AIトレーニングの最先端の可能性を発見してください。AIモデルの究極の可能性を引き出し、仕事に革命を起こしましょう。

XC6SLX4とXC6SLX9:どちらが優れているか?XC6SLX4およびXC6SLX9 FPGAのポテンシャルを活用し、性能と汎用性を強化。

XC6SLX4とXC6SLX9:どちらが優れているか?XC6SLX4およびXC6SLX9 FPGAのポテンシャルを活用し、性能と汎用性を強化。 米国のマイクロコントローラー・メーカー上位10社エレクトロニクスを形作るトッププレーヤーを明らかにする、米国のマイクロコントローラ技術革新トップ10をご覧ください。ゲームを変える旅に出かけよう!

米国のマイクロコントローラー・メーカー上位10社エレクトロニクスを形作るトッププレーヤーを明らかにする、米国のマイクロコントローラ技術革新トップ10をご覧ください。ゲームを変える旅に出かけよう! フィルム対セラミック:適切なコンデンサの選択フィルムコンデンサとセラミックコンデンサを解明しながら、電子部品の世界を探検しましょう。この技術マニア向けのガイドブックで、キャパシタンスの流れを探る魅惑の旅に出かけましょう。

フィルム対セラミック:適切なコンデンサの選択フィルムコンデンサとセラミックコンデンサを解明しながら、電子部品の世界を探検しましょう。この技術マニア向けのガイドブックで、キャパシタンスの流れを探る魅惑の旅に出かけましょう。 米国のRFミキサーメーカートップ10を探るアメリカのRFミキサーメーカートップ10を発見する準備はできましたか?技術革新の旅に出かけましょう。

米国のRFミキサーメーカートップ10を探るアメリカのRFミキサーメーカートップ10を発見する準備はできましたか?技術革新の旅に出かけましょう。 SZComponentsが「国際潜在的スターディストリビューター」賞を受賞賞SZComponentsの「国際的な潜在力を秘めたスター・ディストリビューター」としての目覚ましい受賞を祝い、彼らの成功への道のりを探ります。

SZComponentsが「国際潜在的スターディストリビューター」賞を受賞賞SZComponentsの「国際的な潜在力を秘めたスター・ディストリビューター」としての目覚ましい受賞を祝い、彼らの成功への道のりを探ります。

¥13074.19

価格更新:ヶ月前

Lattice Semiconductor Corporation

ラティスセミコンダクターは低消費電力プログラマビリティをリードし、エッジからクラウドまで、ネットワーク全体の複雑な課題を解決します。通信、コンピューティング、産業、自動車、コンシューマに足がかりを持つラティスセミコンダクターは、持続的な関係を育み、自由なイノベーションのための世界クラスのサポートを提供し、安全で接続された世界を作り上げます。

すべての製品を見る Lattice Semiconductor Corporation人気の商品

ブログ

XC6SLX4とXC6SLX9:どちらが優れているか?XC6SLX4およびXC6SLX9 FPGAのポテンシャルを活用し、性能と汎用性を強化。

XC6SLX4とXC6SLX9:どちらが優れているか?XC6SLX4およびXC6SLX9 FPGAのポテンシャルを活用し、性能と汎用性を強化。 米国のマイクロコントローラー・メーカー上位10社エレクトロニクスを形作るトッププレーヤーを明らかにする、米国のマイクロコントローラ技術革新トップ10をご覧ください。ゲームを変える旅に出かけよう!

米国のマイクロコントローラー・メーカー上位10社エレクトロニクスを形作るトッププレーヤーを明らかにする、米国のマイクロコントローラ技術革新トップ10をご覧ください。ゲームを変える旅に出かけよう! フィルム対セラミック:適切なコンデンサの選択フィルムコンデンサとセラミックコンデンサを解明しながら、電子部品の世界を探検しましょう。この技術マニア向けのガイドブックで、キャパシタンスの流れを探る魅惑の旅に出かけましょう。

フィルム対セラミック:適切なコンデンサの選択フィルムコンデンサとセラミックコンデンサを解明しながら、電子部品の世界を探検しましょう。この技術マニア向けのガイドブックで、キャパシタンスの流れを探る魅惑の旅に出かけましょう。 米国のRFミキサーメーカートップ10を探るアメリカのRFミキサーメーカートップ10を発見する準備はできましたか?技術革新の旅に出かけましょう。

米国のRFミキサーメーカートップ10を探るアメリカのRFミキサーメーカートップ10を発見する準備はできましたか?技術革新の旅に出かけましょう。 SZComponentsが「国際潜在的スターディストリビューター」賞を受賞賞SZComponentsの「国際的な潜在力を秘めたスター・ディストリビューター」としての目覚ましい受賞を祝い、彼らの成功への道のりを探ります。

SZComponentsが「国際潜在的スターディストリビューター」賞を受賞賞SZComponentsの「国際的な潜在力を秘めたスター・ディストリビューター」としての目覚ましい受賞を祝い、彼らの成功への道のりを探ります。

未来を解き明かす:2024年に急増するマイコンダイナミックな電子部品の世界において、マイクロコントローラは革新性と汎用性の証として際立っています。2024年に近づくにつれ、STマイクロエレクトロニクス、テキサス・インスツルメンツ、マイクロチップなどの大企業が先導するマイクロコントローラと半導体の状況は、著しい変化を遂げようとしています。

未来を解き明かす:2024年に急増するマイコンダイナミックな電子部品の世界において、マイクロコントローラは革新性と汎用性の証として際立っています。2024年に近づくにつれ、STマイクロエレクトロニクス、テキサス・インスツルメンツ、マイクロチップなどの大企業が先導するマイクロコントローラと半導体の状況は、著しい変化を遂げようとしています。 マイクロコントローラ vs. マイクロプロセッサ:組込みシステム工学のためのコアの違いを解き明かす組込みシステムエンジニアリングやエレクトロニクス分野の製品開発に精通した専門家は、マイクロコントローラとマイクロプロセッサの区別に悩むことが多い。無数の電子機器の設計と製造において基本的な役割を担っているにもかかわらず、単なる定義に基づいてその独自の機能を理解することは困難です:

マイクロコントローラ vs. マイクロプロセッサ:組込みシステム工学のためのコアの違いを解き明かす組込みシステムエンジニアリングやエレクトロニクス分野の製品開発に精通した専門家は、マイクロコントローラとマイクロプロセッサの区別に悩むことが多い。無数の電子機器の設計と製造において基本的な役割を担っているにもかかわらず、単なる定義に基づいてその独自の機能を理解することは困難です: セラミックコンデンサの世界市場を深堀する世界のセラミックコンデンサ市場における環境意識の新たなサブプロットを探る。

セラミックコンデンサの世界市場を深堀する世界のセラミックコンデンサ市場における環境意識の新たなサブプロットを探る。 マイクロコントローラで電流測定をマスターするマイクロコントローラーで正確な電流測定の秘密を解き明かす!オンチップ・アナログ・コア独立ペリフェラル(CIP)で課題を克服し、超人的なソリューションを実現し、精度に革命をもたらします。

マイクロコントローラで電流測定をマスターするマイクロコントローラーで正確な電流測定の秘密を解き明かす!オンチップ・アナログ・コア独立ペリフェラル(CIP)で課題を克服し、超人的なソリューションを実現し、精度に革命をもたらします。 整流ダイオードとは?初心者向けガイドエレクトロニクスの縁の下の力持ち、整流ダイオード!整流ダイオードの魔力、アプリケーションを探求し、ガジェット・パワーへの舞台裏の冒険に参加しよう。

整流ダイオードとは?初心者向けガイドエレクトロニクスの縁の下の力持ち、整流ダイオード!整流ダイオードの魔力、アプリケーションを探求し、ガジェット・パワーへの舞台裏の冒険に参加しよう。

FPGA対決:XC6SLX16 vs XC6SLX25クイックガイドでFPGAの秘密を解き明かすXC6SLX16とXC6SLX25、次の技術的冒険の鍵はどちらに?今すぐクリックして、プログラマブルな可能性の世界を探検してください!

FPGA対決:XC6SLX16 vs XC6SLX25クイックガイドでFPGAの秘密を解き明かすXC6SLX16とXC6SLX25、次の技術的冒険の鍵はどちらに?今すぐクリックして、プログラマブルな可能性の世界を探検してください! オンセミの先進画像センサーで交通安全を強化onsemiのAR0220ATは、先進運転支援システムの夜間の常識を覆します。

オンセミの先進画像センサーで交通安全を強化onsemiのAR0220ATは、先進運転支援システムの夜間の常識を覆します。 テキサス・インスツルメンツ、ユタ州リーハイを最先端半導体ハブに選定テキサス・インスツルメンツ(TI)社は、ユタ州リーハイを300ミリ半導体ウェハ製造工場(ファブ)の建設予定地に選んだ。

テキサス・インスツルメンツ、ユタ州リーハイを最先端半導体ハブに選定テキサス・インスツルメンツ(TI)社は、ユタ州リーハイを300ミリ半導体ウェハ製造工場(ファブ)の建設予定地に選んだ。 SZComponentsからの感謝祭のご挨拶SZComponentsファミリーの一員であることに感謝します。感謝祭おめでとうございます!

SZComponentsからの感謝祭のご挨拶SZComponentsファミリーの一員であることに感謝します。感謝祭おめでとうございます! AIモデル・トレーニングのためのNvidia H200のパワーを発見するNvidiaのH200チップで、AIトレーニングの最先端の可能性を発見してください。AIモデルの究極の可能性を引き出し、仕事に革命を起こしましょう。

AIモデル・トレーニングのためのNvidia H200のパワーを発見するNvidiaのH200チップで、AIトレーニングの最先端の可能性を発見してください。AIモデルの究極の可能性を引き出し、仕事に革命を起こしましょう。

XC6SLX4とXC6SLX9:どちらが優れているか?XC6SLX4およびXC6SLX9 FPGAのポテンシャルを活用し、性能と汎用性を強化。

XC6SLX4とXC6SLX9:どちらが優れているか?XC6SLX4およびXC6SLX9 FPGAのポテンシャルを活用し、性能と汎用性を強化。 米国のマイクロコントローラー・メーカー上位10社エレクトロニクスを形作るトッププレーヤーを明らかにする、米国のマイクロコントローラ技術革新トップ10をご覧ください。ゲームを変える旅に出かけよう!

米国のマイクロコントローラー・メーカー上位10社エレクトロニクスを形作るトッププレーヤーを明らかにする、米国のマイクロコントローラ技術革新トップ10をご覧ください。ゲームを変える旅に出かけよう! フィルム対セラミック:適切なコンデンサの選択フィルムコンデンサとセラミックコンデンサを解明しながら、電子部品の世界を探検しましょう。この技術マニア向けのガイドブックで、キャパシタンスの流れを探る魅惑の旅に出かけましょう。

フィルム対セラミック:適切なコンデンサの選択フィルムコンデンサとセラミックコンデンサを解明しながら、電子部品の世界を探検しましょう。この技術マニア向けのガイドブックで、キャパシタンスの流れを探る魅惑の旅に出かけましょう。 米国のRFミキサーメーカートップ10を探るアメリカのRFミキサーメーカートップ10を発見する準備はできましたか?技術革新の旅に出かけましょう。

米国のRFミキサーメーカートップ10を探るアメリカのRFミキサーメーカートップ10を発見する準備はできましたか?技術革新の旅に出かけましょう。 SZComponentsが「国際潜在的スターディストリビューター」賞を受賞賞SZComponentsの「国際的な潜在力を秘めたスター・ディストリビューター」としての目覚ましい受賞を祝い、彼らの成功への道のりを探ります。

SZComponentsが「国際潜在的スターディストリビューター」賞を受賞賞SZComponentsの「国際的な潜在力を秘めたスター・ディストリビューター」としての目覚ましい受賞を祝い、彼らの成功への道のりを探ります。

未来を解き明かす:2024年に急増するマイコンダイナミックな電子部品の世界において、マイクロコントローラは革新性と汎用性の証として際立っています。2024年に近づくにつれ、STマイクロエレクトロニクス、テキサス・インスツルメンツ、マイクロチップなどの大企業が先導するマイクロコントローラと半導体の状況は、著しい変化を遂げようとしています。

未来を解き明かす:2024年に急増するマイコンダイナミックな電子部品の世界において、マイクロコントローラは革新性と汎用性の証として際立っています。2024年に近づくにつれ、STマイクロエレクトロニクス、テキサス・インスツルメンツ、マイクロチップなどの大企業が先導するマイクロコントローラと半導体の状況は、著しい変化を遂げようとしています。 マイクロコントローラ vs. マイクロプロセッサ:組込みシステム工学のためのコアの違いを解き明かす組込みシステムエンジニアリングやエレクトロニクス分野の製品開発に精通した専門家は、マイクロコントローラとマイクロプロセッサの区別に悩むことが多い。無数の電子機器の設計と製造において基本的な役割を担っているにもかかわらず、単なる定義に基づいてその独自の機能を理解することは困難です:

マイクロコントローラ vs. マイクロプロセッサ:組込みシステム工学のためのコアの違いを解き明かす組込みシステムエンジニアリングやエレクトロニクス分野の製品開発に精通した専門家は、マイクロコントローラとマイクロプロセッサの区別に悩むことが多い。無数の電子機器の設計と製造において基本的な役割を担っているにもかかわらず、単なる定義に基づいてその独自の機能を理解することは困難です: セラミックコンデンサの世界市場を深堀する世界のセラミックコンデンサ市場における環境意識の新たなサブプロットを探る。

セラミックコンデンサの世界市場を深堀する世界のセラミックコンデンサ市場における環境意識の新たなサブプロットを探る。 マイクロコントローラで電流測定をマスターするマイクロコントローラーで正確な電流測定の秘密を解き明かす!オンチップ・アナログ・コア独立ペリフェラル(CIP)で課題を克服し、超人的なソリューションを実現し、精度に革命をもたらします。

マイクロコントローラで電流測定をマスターするマイクロコントローラーで正確な電流測定の秘密を解き明かす!オンチップ・アナログ・コア独立ペリフェラル(CIP)で課題を克服し、超人的なソリューションを実現し、精度に革命をもたらします。 整流ダイオードとは?初心者向けガイドエレクトロニクスの縁の下の力持ち、整流ダイオード!整流ダイオードの魔力、アプリケーションを探求し、ガジェット・パワーへの舞台裏の冒険に参加しよう。

整流ダイオードとは?初心者向けガイドエレクトロニクスの縁の下の力持ち、整流ダイオード!整流ダイオードの魔力、アプリケーションを探求し、ガジェット・パワーへの舞台裏の冒険に参加しよう。

FPGA対決:XC6SLX16 vs XC6SLX25クイックガイドでFPGAの秘密を解き明かすXC6SLX16とXC6SLX25、次の技術的冒険の鍵はどちらに?今すぐクリックして、プログラマブルな可能性の世界を探検してください!

FPGA対決:XC6SLX16 vs XC6SLX25クイックガイドでFPGAの秘密を解き明かすXC6SLX16とXC6SLX25、次の技術的冒険の鍵はどちらに?今すぐクリックして、プログラマブルな可能性の世界を探検してください! オンセミの先進画像センサーで交通安全を強化onsemiのAR0220ATは、先進運転支援システムの夜間の常識を覆します。

オンセミの先進画像センサーで交通安全を強化onsemiのAR0220ATは、先進運転支援システムの夜間の常識を覆します。 テキサス・インスツルメンツ、ユタ州リーハイを最先端半導体ハブに選定テキサス・インスツルメンツ(TI)社は、ユタ州リーハイを300ミリ半導体ウェハ製造工場(ファブ)の建設予定地に選んだ。

テキサス・インスツルメンツ、ユタ州リーハイを最先端半導体ハブに選定テキサス・インスツルメンツ(TI)社は、ユタ州リーハイを300ミリ半導体ウェハ製造工場(ファブ)の建設予定地に選んだ。 SZComponentsからの感謝祭のご挨拶SZComponentsファミリーの一員であることに感謝します。感謝祭おめでとうございます!

SZComponentsからの感謝祭のご挨拶SZComponentsファミリーの一員であることに感謝します。感謝祭おめでとうございます! AIモデル・トレーニングのためのNvidia H200のパワーを発見するNvidiaのH200チップで、AIトレーニングの最先端の可能性を発見してください。AIモデルの究極の可能性を引き出し、仕事に革命を起こしましょう。

AIモデル・トレーニングのためのNvidia H200のパワーを発見するNvidiaのH200チップで、AIトレーニングの最先端の可能性を発見してください。AIモデルの究極の可能性を引き出し、仕事に革命を起こしましょう。

XC6SLX4とXC6SLX9:どちらが優れているか?XC6SLX4およびXC6SLX9 FPGAのポテンシャルを活用し、性能と汎用性を強化。

XC6SLX4とXC6SLX9:どちらが優れているか?XC6SLX4およびXC6SLX9 FPGAのポテンシャルを活用し、性能と汎用性を強化。 米国のマイクロコントローラー・メーカー上位10社エレクトロニクスを形作るトッププレーヤーを明らかにする、米国のマイクロコントローラ技術革新トップ10をご覧ください。ゲームを変える旅に出かけよう!

米国のマイクロコントローラー・メーカー上位10社エレクトロニクスを形作るトッププレーヤーを明らかにする、米国のマイクロコントローラ技術革新トップ10をご覧ください。ゲームを変える旅に出かけよう! フィルム対セラミック:適切なコンデンサの選択フィルムコンデンサとセラミックコンデンサを解明しながら、電子部品の世界を探検しましょう。この技術マニア向けのガイドブックで、キャパシタンスの流れを探る魅惑の旅に出かけましょう。

フィルム対セラミック:適切なコンデンサの選択フィルムコンデンサとセラミックコンデンサを解明しながら、電子部品の世界を探検しましょう。この技術マニア向けのガイドブックで、キャパシタンスの流れを探る魅惑の旅に出かけましょう。 米国のRFミキサーメーカートップ10を探るアメリカのRFミキサーメーカートップ10を発見する準備はできましたか?技術革新の旅に出かけましょう。

米国のRFミキサーメーカートップ10を探るアメリカのRFミキサーメーカートップ10を発見する準備はできましたか?技術革新の旅に出かけましょう。 SZComponentsが「国際潜在的スターディストリビューター」賞を受賞賞SZComponentsの「国際的な潜在力を秘めたスター・ディストリビューター」としての目覚ましい受賞を祝い、彼らの成功への道のりを探ります。

SZComponentsが「国際潜在的スターディストリビューター」賞を受賞賞SZComponentsの「国際的な潜在力を秘めたスター・ディストリビューター」としての目覚ましい受賞を祝い、彼らの成功への道のりを探ります。

人気のメーカー

View all manufactures もっと人気の部品番号

その他の電子部品 もっと

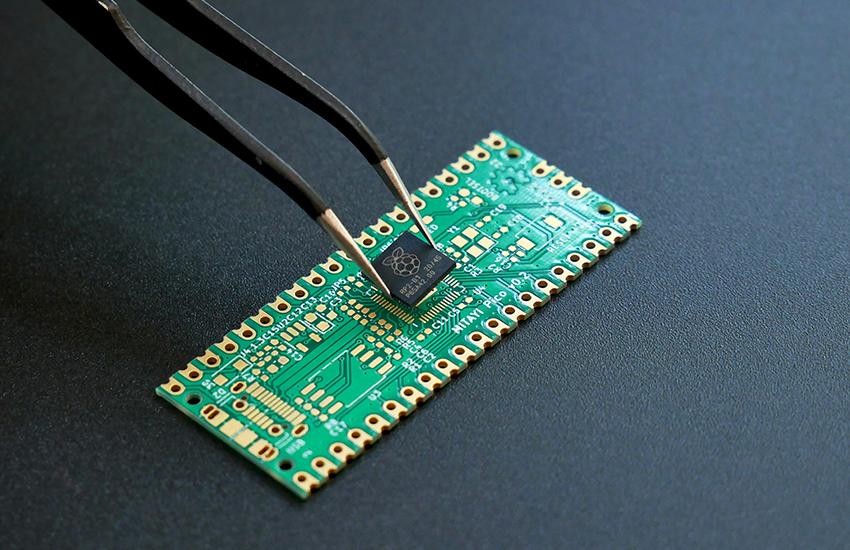

LCMXO2-1200ZE-P1-EVN

KIT DEVELOPMENT MACHXO2 PICO

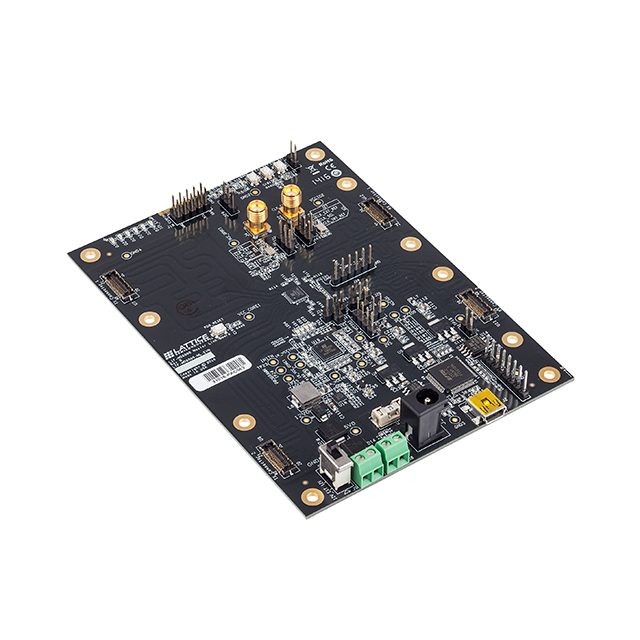

LIFCL-VIP-SI-EVN

BRD EV VIP SENS INPUT CRSLINK-NX

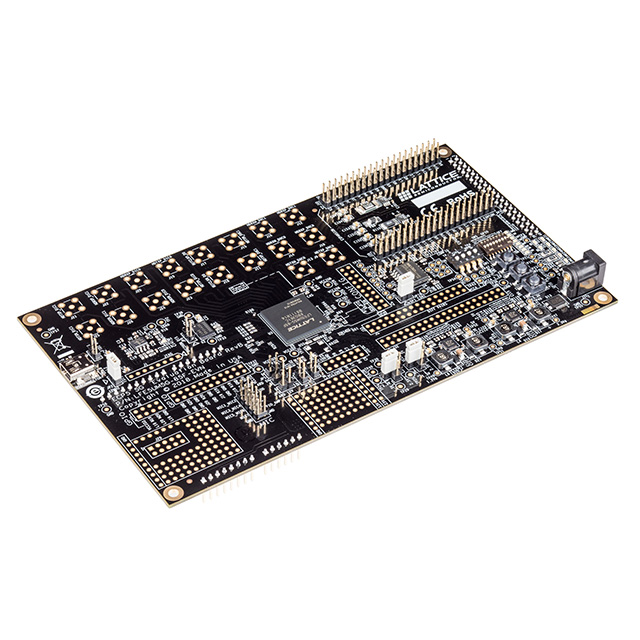

LCMXO3LF-6900C-S-EVN

STARTER KIT MACHXO3LF

ICE40UP5K-B-EVN

ICE40 ULTRAPLUS BREAKOUT BOARD

LIF-MD6000-ML-EVN

CROSSLINK LIF-MD6000 MASTER LINK

LFE5UM5G-85F-EVN

ECP5 EVALUATION BOARD

LFXP2-5E-B2-EVN

KIT DEV LATTICE XP2 BREVIA2

LC4256ZE-B-EVN

BOARD BREAKOUT ISPMACH 4256ZE

LFE5UM5G-45F-VERSA-EVN

ECP5-5G VERSA DEVELOPMENT KIT -

ICE5LP4K-WDEV-EVN

DEV PLATFORM WEARABLE SCREEN